Radio Frequency Circuit Design. W. Alan Davis, Krishna Agarwal Copyright © 2001 John Wiley & Sons, Inc. Print ISBN 0-471-35052-4 Electronic ISBN 0-471-20068-9

### Radio Frequency Circuit Design

### WILEY SERIES IN MICROWAVE AND OPTICAL ENGINEERING

KAI CHANG, Editor Texas A&M University

A complete list of the titles in this series appears at the end of this volume.

# Radio Frequency Circuit Design

**W. ALAN DAVIS** University of Texas at Arlington

**KRISHNA AGARWAL** *Raytheon Systems Company*

Designations used by companies to distinguish their products are often claimed as trademarks. In all instances where John Wiley & Sons, Inc., is aware of a claim, the product names appear in initial capital or ALL CAPITAL LETTERS. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

Copyright © 2001 by John Wiley & Sons, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic or mechanical, including uploading, downloading, printing, decompiling, recording or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without the prior written permission of the Publisher. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ@WILEY.COM.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional person should be sought.

#### ISBN 0-471-20068-9.

This title is also available in print as ISBN 0-471-35052-4.

For more information about Wiley products, visit our web site at www.Wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

Davis, W. Alan.

Radio frequency circuit design / W. Alan Davis, Krishna Agarwal.

p. cm. — (Wiley series in microwave and optical engineering)

Includes index.

ISBN 0-471-35052-4

1. Radio circuits — Design and construction. I. Agarwal, Krishna K. (Krishna Kumar)

II. Title. III. Series.

TK6560 .D38 2001 621.381'32 — dc21

00-043690

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

Dedicated to our wives, Margaret Davis, Elisabeth Agarwal and our children: Brent, Nathan, Janelle Davis Sareeta, Sandeep, Suneet Agarwal

# Contents

| Preface                                      | xiii |

|----------------------------------------------|------|

| 1 Communication Channel                      | 1    |

| 1.1 Basic Transmitter–Receiver Configuration | 1    |

| 1.2 Information and Capacity                 | 3    |

| 1.3 Dependent States                         | 6    |

| Problems                                     | 8    |

| References                                   | 8    |

| 2 Resistors, Capacitors, and Inductors       | 9    |

| 2.1 Introduction                             | 9    |

| 2.2 Resistors                                | 9    |

| 2.3 Capacitors                               | 14   |

| 2.4 Inductors                                | 20   |

| Problems                                     | 31   |

| References                                   | 31   |

| 3 Impedance Matching                         | 33   |

| 3.1 Introduction                             | 33   |

| 3.2 The $Q$ Factor                           | 33   |

| 3.3 Resonance and Bandwidth                  | 34   |

| 3.4 Unloaded Q                               | 36   |

| 3.5 L Circuit Impedance Matching             | 36   |

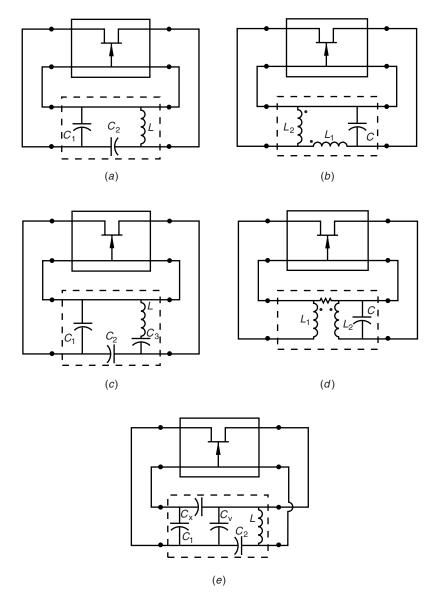

| 3.6 $\pi$ Transformation Circuit             | 39   |

| 3.7 T Transformation Circuit                 | 41   |

| 3.8 Tapped Capacitor Transformer             | 42   |

| 3.9 Parallel Double-Tuned Transformer        | 45   |

| Problems                                     | 49   |

| References                                   | 50   |

|                                              |      |

| 4 | Multiport Circuit Parameters and Transmission Lines  | 51  |

|---|------------------------------------------------------|-----|

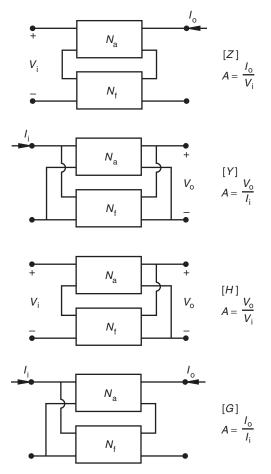

|   | 4.1 Voltage–Current Two-Port Parameters              | 51  |

|   | 4.2 ABCD Parameters                                  | 53  |

|   | 4.3 Image Impedance                                  | 54  |

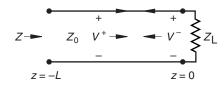

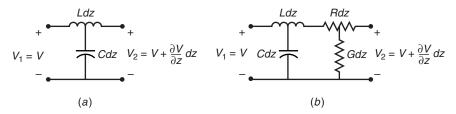

|   | 4.4 The Telegrapher's Equations                      | 59  |

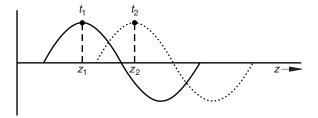

|   | 4.5 The Transmission Line Equation                   | 61  |

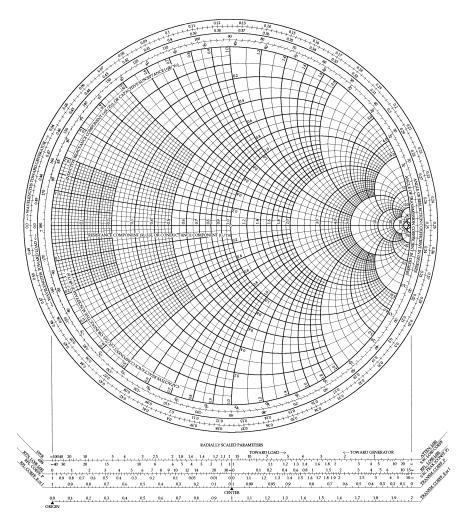

|   | 4.6 The Smith Chart                                  | 63  |

|   | 4.7 Commonly Used Transmission Lines                 | 65  |

|   | 4.8 Scattering Parameters                            | 74  |

|   | 4.9 The Indefinite Admittance Matrix                 | 78  |

|   | 4.10 The Indefinite Scattering Matrix                | 80  |

|   | Problems                                             | 82  |

|   | References                                           | 82  |

| 5 | Filter Design and Approximation                      | 84  |

|   | 5.1 Introduction                                     | 84  |

|   | 5.2 Ideal and Approximate Filter Types               | 84  |

|   | 5.3 Transfer Function and Basic Filter Concepts      | 88  |

|   | 5.4 Ladder Network Filters                           | 89  |

|   | 5.5 The Elliptic Filter                              | 94  |

|   | 5.6 Matching between Unequal Resistances             | 95  |

|   | Problems                                             | 104 |

|   | References                                           | 104 |

| 6 | Transmission Line Transformers                       | 105 |

|   | 6.1 Introduction                                     | 105 |

|   | 6.2 Ideal Transmission Line Transformers             | 106 |

|   | 6.3 Transmission Line Transformer Synthesis          | 110 |

|   | 6.4 Electrically Long Transmission Line Transformers | 111 |

|   | 6.5 Baluns                                           | 115 |

|   | 6.6 Dividers And Combiners                           | 117 |

|   | Problems                                             | 121 |

|   | References                                           | 121 |

| 7 | Class A Amplifiers                                   | 122 |

|   | 7.1 Introduction                                     | 122 |

|   | 7.2 Definition of Gain [2]                           | 122 |

|   | 7.3 Transducer Power Gain of a Two-Port              | 123 |

|   | 7.4 Power Gain Using S Parameters                    | 124 |

|   | 7.5 Simultaneous Match for Maximum Power Gain        | 127 |

|   | 7.6 Stability                                        | 129 |

|   | 7.7 Class A Power Amplifiers                         | 139 |

|   | L L                                                  |     |

| 7.8       | Power Combining of Power Amplifiers                | 141 |

|-----------|----------------------------------------------------|-----|

|           | Problems                                           | 142 |

|           | References                                         | 143 |

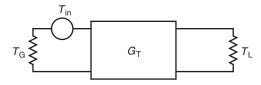

| 8 Noise   |                                                    | 144 |

| 8.1       | Sources of Noise                                   | 144 |

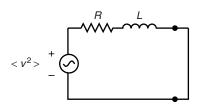

| 8.2       | Thermal Noise                                      | 145 |

| 8.3       | Shot Noise                                         | 148 |

| 8.4       | Noise Circuit Analysis                             | 149 |

| 8.5       | Amplifier Noise Characterization                   | 151 |

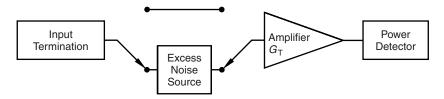

| 8.6       | Noise Measurement                                  | 152 |

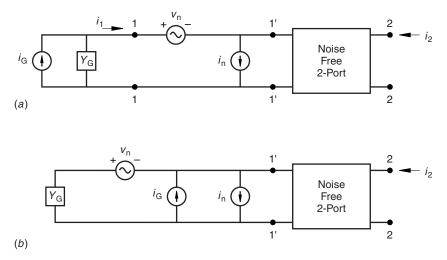

| 8.7       | Noisy Two-Ports                                    | 153 |

|           | Two-Port Noise Figure Derivation                   | 154 |

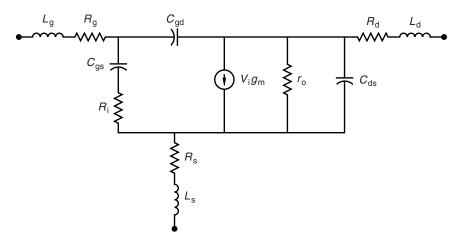

| 8.9       | The Fukui Noise Model for Transistors              | 158 |

| 8.10      | Properties of Cascaded Amplifiers                  | 161 |

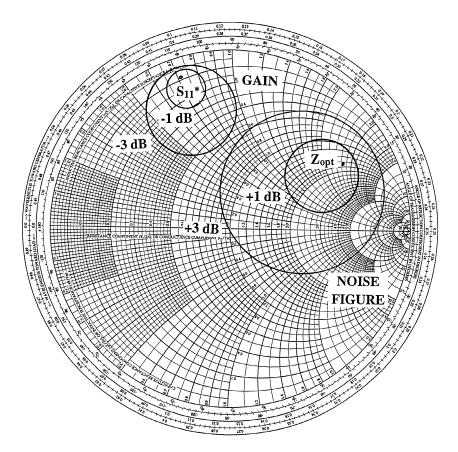

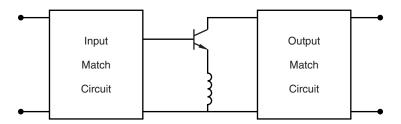

| 8.11      | Amplifier Design for Optimum Gain and Noise        | 164 |

|           | Problems                                           | 166 |

|           | References                                         | 166 |

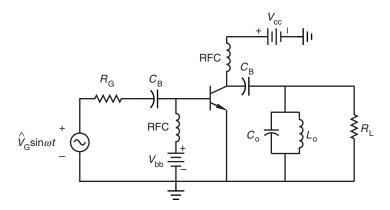

| 9 RF P    | ower Amplifiers                                    | 168 |

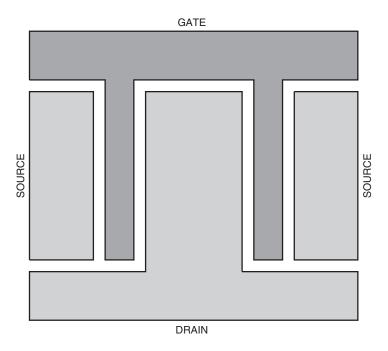

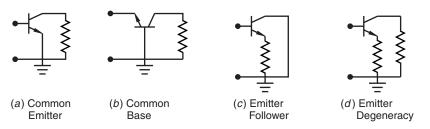

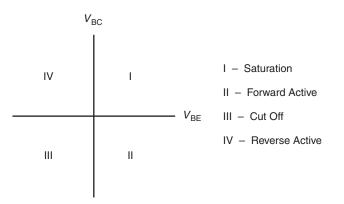

| 9.1       | Transistor Configurations                          | 168 |

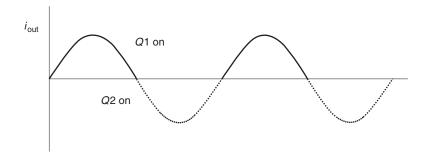

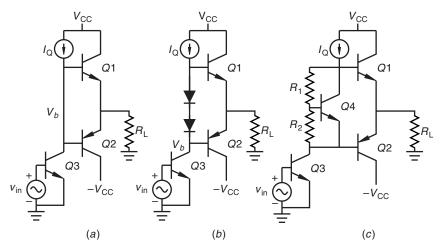

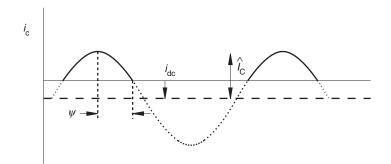

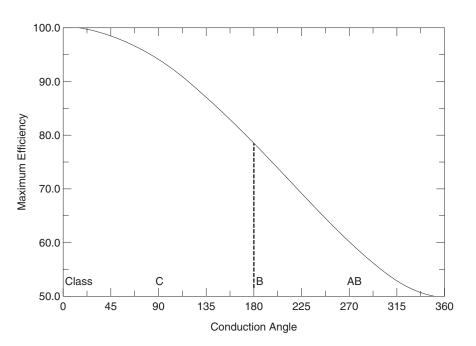

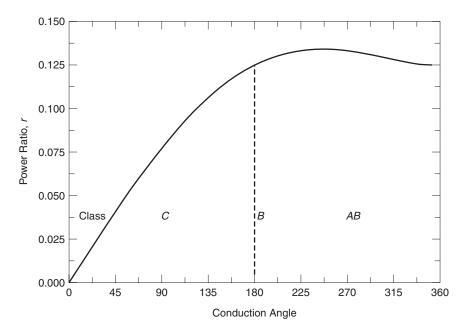

|           | The Class B Amplifier                              | 169 |

|           | The Class C Amplifier                              | 178 |

|           | Class C Input Bias Voltage                         | 183 |

|           | The Class D Power Amplifier                        | 184 |

| 9.6       | The Class F Power Amplifier                        | 185 |

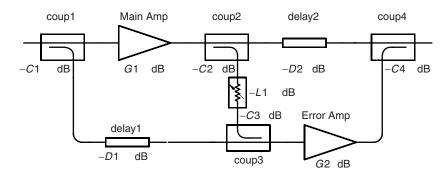

| 9.7       | Feed-Forward Amplifiers                            | 191 |

|           | Problems                                           | 193 |

|           | References                                         | 193 |

| 10 Oscill | ators and Harmonic Generators                      | 195 |

| 10.1      | Oscillator Fundamentals                            | 195 |

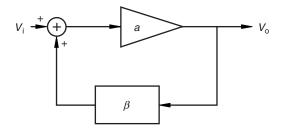

| 10.2      | Feedback Theory                                    | 197 |

| 10.3      | Two-Port Oscillators with External Feedback        | 197 |

| 10.4      | Practical Oscillator Example                       | 202 |

| 10.5      | Minimum Requirements of the Reflection Coefficient | 204 |

| 10.6      | Common Gate (Base) Oscillators                     | 206 |

| 10.7      | Stability of an Oscillator                         | 210 |

|           | Injection-Locked Oscillators                       | 214 |

| 10.9      | Harmonic Generators                                | 216 |

|           | Problems                                           | 221 |

|           | References                                         | 221 |

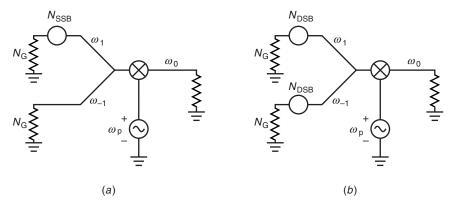

| 11 | RF Mixers                                               | 222 |

|----|---------------------------------------------------------|-----|

|    | 11.1 Nonlinear Device Characteristics                   | 222 |

|    | 11.2 Figures of Merit for Mixers                        | 226 |

|    | 11.3 Single-Ended Mixers                                | 227 |

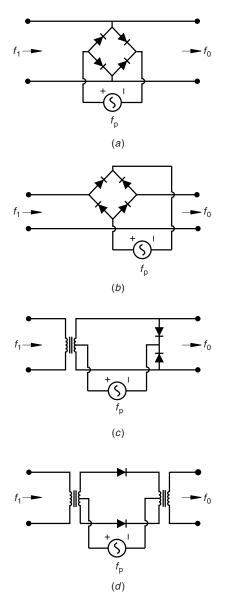

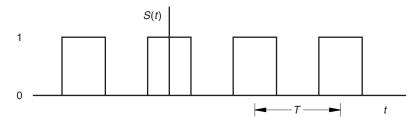

|    | 11.4 Single-Balanced Mixers                             | 228 |

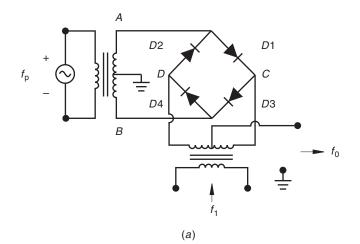

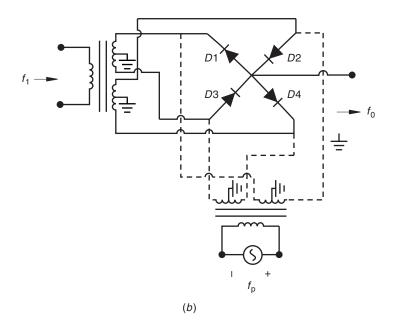

|    | 11.5 Double-Balanced Mixers                             | 230 |

|    | 11.6 Double-Balanced Transistor Mixers                  | 235 |

|    | 11.7 Spurious Response                                  | 240 |

|    | 11.8 Single-Sideband Noise Figure and Noise Temperature | 243 |

|    | Problems                                                | 246 |

|    | References                                              | 246 |

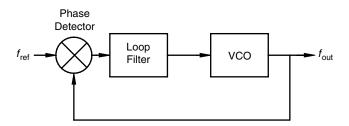

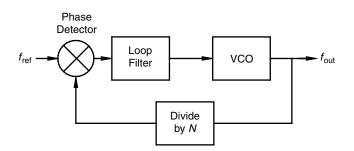

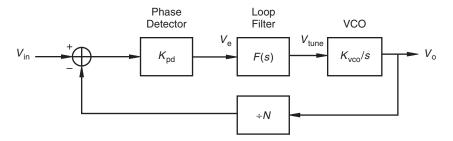

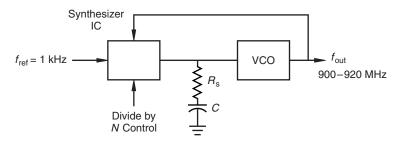

| 12 | Phase Lock Loops                                        | 247 |

|    | 12.1 Introduction                                       | 247 |

|    | 12.2 PLL Design Background                              | 247 |

|    | 12.3 PLL Applications                                   | 248 |

|    | 12.4 PLL Basics                                         | 249 |

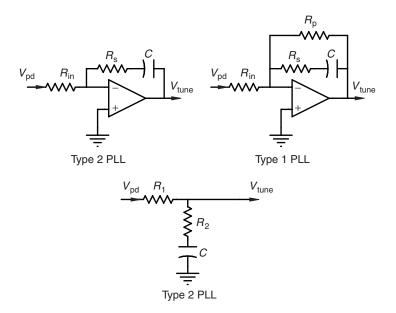

|    | 12.5 Loop Design Principles                             | 250 |

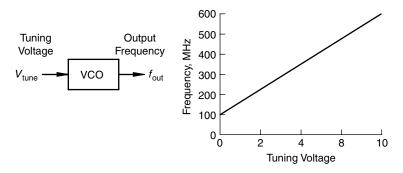

|    | 12.6 PLL Components                                     | 251 |

|    | 12.7 Linear Analysis of the PLL [1]                     | 255 |

|    | 12.8 Locking a Phase Lock Loop                          | 259 |

|    | 12.9 Loop Types                                         | 261 |

|    | 12.10 Negative Feedback in a PLL                        | 263 |

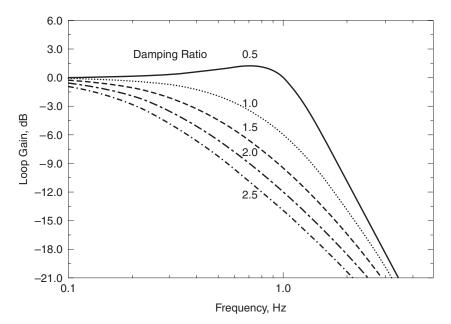

|    | 12.11 PLL Design Equations                              | 264 |

|    | 12.12 PLL Oscillators                                   | 270 |

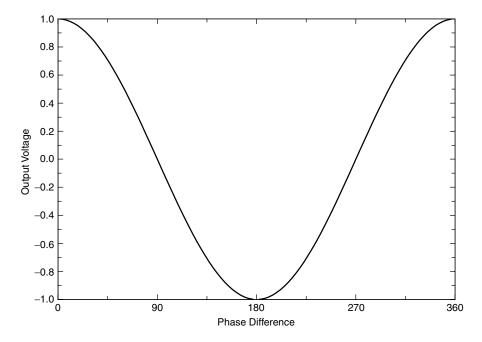

|    | 12.13 Phase Detector Types                              | 271 |

|    | 12.14 Design Examples                                   | 274 |

|    | Problems                                                | 277 |

|    | References                                              | 277 |

| 13 | Emerging Technology                                     | 278 |

|    | 13.1 Introduction                                       | 278 |

|    | 13.2 Bandwidth                                          | 280 |

|    | 13.3 Spectrum Conservation                              | 280 |

|    | 13.4 Mobility                                           | 281 |

|    | 13.5 Wireless Internet Access                           | 282 |

|    | 13.6 Key Technologies                                   | 283 |

|    | References                                              | 284 |

| Ap | opendixes                                               |     |

| A. | Example of a Solenoid Design                            | 285 |

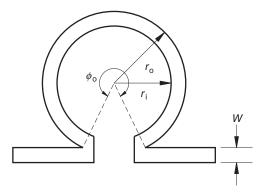

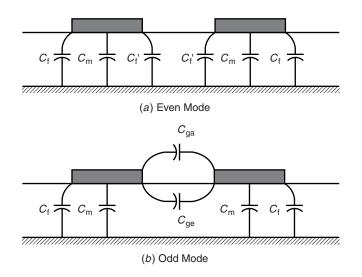

| B. | Analytical Spiral Inductor Model                        | 286 |

| Ind | ex                                                                               | 323 |

|-----|----------------------------------------------------------------------------------|-----|

| H.  | Single-Tone Intermodulation Distortion<br>Suppression for Double-Balanced Mixers | 319 |

| G.  | Transformed Frequency Domain Measurements<br>Using Spice                         | 305 |

| F.  | Transistor and Amplifier Formulas                                                | 300 |

| E.  | Termination of a Transistor Port with a Load                                     | 296 |

| D.  | Two-Port Parameter Conversion                                                    | 292 |

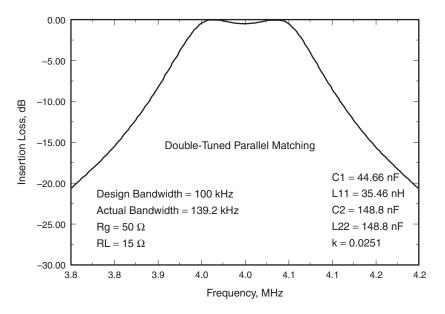

| C.  | Double-Tuned Matching Circuit Example                                            | 290 |

# Preface

The cellular telephone has become a symbol for the rapid change in the communications business. Within this plastic container reside the talents of engineers working in the areas of efficient power supplies, digital circuit design, analog circuit design, semiconductor device design, antennas, linear systems, digital signal processing, packaging, and materials science. All these talents are carefully coordinated at a cost that allows a wide cross section of the world's population to have available instant communication. The particular aspect of all these activities that is of primary focus in this text is in the area of analog circuit design, with primary emphasis on radio frequency electronics. Some topics normally considered in electronics courses or in microwave and antenna courses are not covered here. For example, there is no mention of distributed branch line couplers, since at 1 GHz their size would be prohibitive. On the other hand, topics such as transmission line transformers are covered because they fit so well into this frequency range.

This book is meant for readers who have at least advanced standing in electrical engineering. The material in this text has been taught as a senior and graduate-level course in radio frequency circuit design at the University of Texas at Arlington. This class has continued to be popular for the past 20 years under the guidance of at least four different instructors, two of whom are the present authors. Because of the activity in the communications area, there has been ever greater interest in this subject. It is the intent of the authors, therefore, to update the current text offerings while at the same time avoiding simply reworking a microwave text.

The authors gratefully acknowledge the contribution of Michael Black, Raytheon Systems Company, to the phase lock loop discussion in Chapter 12.

> W. Alan Davis Krishna Agarwal

# Index

ABCD matrix, see ABCD parameters

ABCD parameters, 30, 53–56, 58, 74, 154

Active filter, 84

Active load, 13

Actual noise figure, 151

Admittance parameters, see y parameters

AM, 3, 4

Ampère's law, 67, 69

AMPS, 278

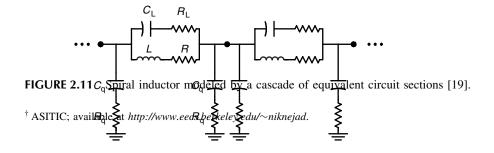

ASITIC, 27

Available gain, 122

B-ISDN, 279 Balun(s), 115–118 Bandwidth efficiency, 1 Bandwidth, 35, 47, 159, 178, 280 Barkhausen criterion, 195, 197, 201 Beat note, 252, 259–261, 263, 271 Black body radiation, 145 Bluetooth, 283 Boltzmann probability, 145 Butterworth, 89–90, 92, 95–97

Capacitance fringing, 29–30 Capacitor resonances, 17 alumina, 16 BaTiO<sub>3</sub>, 16–17 coupled microstrip, 26 hybrid, 14–15, 20 interdigital, 18 loss, 15–19

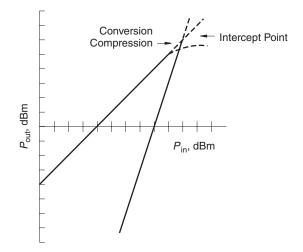

metal - insulator - metal, 18 monolithic, 14, 17, 20 NPO, 16-17 Porcelain, 16-17 Capacity, 3, 5-7 Cascaded amplifiers, 161 Cauer extraction, 97 CDMA, 3, 279-280, 282 Channel, 4 Characteristic admittance, 154 Characteristic impedance, 61–62, 65, 67, 72-73, 77-78, 102-103, 106, 114, 119-120, 154, 205, 289, 294, 306, 309 **CHEBY**, 102 Chebyshev, 90-92, 94-96, 98, 102 Circuit Q, 33, 44 Class A amplifier(s), 3, 122, 168, 181 Class A power amplifier(s), 139 Class AB amplifier(s), 3 Class B amplifier(s), 169–171, 173, 175-177, 181 Class C amplifier(s), 3, 178–179, 181-183, 188 Class D amplifier, 184 Class F amplifier, 185-186, 188 Coaxial transmission line, 67-68, 115 Collector efficiency, 185 Combiner(s), 117-118 Combining, power 141–142 COMSAT, 283 Conduction angle, 169, 170, 178-179, 183 - 184Conductivity, 9-10 Conductor loss, 70-71, 73 Conversion compression, 227, 242

Conversion gain, 243 Conversion loss, 226 Convolution, 225-226 Curvilinear squares, 12 Cutoff frequency, 85 Damping factor, see Damping ratio Damping ratio, 247, 250, 265-267, 269, 276Darlington method, 99 Darlington procedure, 95, 97, 103 DBLTUNE, 49, 290 DCS, 278 **DECT**, 279 Dependent states, 6 Dielectric loss, 69, 71, 73 Discontinuities, 309, 311, 313 Divider(s), 117 frequency, 251, 255, 259 Double tuned circuit, 45-47, 290-291 DSB, see Noise DSP, 279, 283 Dynamic range, 144, 227, 230, 242-243 Effective dielectric constant, 71–73, 289 Efficiency, 122, 139, 141, 162, 164, 168-169, 176-178, 180-185, 217, 218 multistage amplifier, 163 power added, 189, 191 ELLIPTIC, 94 Elliptic filter, 94 Error voltage, 254, 261 Even mode voltage, 28–29 Even-mode current, 106 Exchangeable gain, 122 FCC, 278, 282 FDMA, 3, 280 Feed-forward amplifier(s), 191-192 Feedback, 129, 136–138, 161, 191, 195-197, 200, 202, 206, 209, 247, 250, 261, 263 Filter(s) all pass, 86-87, 94 bandpass, 86-87, 89, 101-102 bandstop, 86-87, 89, 101 high pass, 86–87, 89, 100 ideal, 85, 89 low pass, 85–87, 89, 94–95, 100-102, 228, 258, 262 low pass prototype, 89-90, 92-93, 99-101

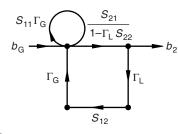

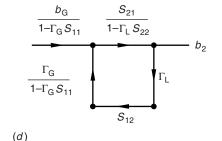

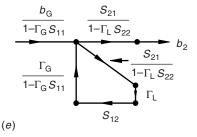

Final value theorem, 259 Flow graph, 125 FM, 3 Fourier transform, 225-226, 232 Fractional bandwidth, 101–102 Friis formula, 162-163, 281 FSK, 279 Fukui equations, 161 Fukui noise model, 158 g parameters, 52, 74, 132, 197, 292 Generators, harmonic, 216 GMSK, 279 GPRS, 282 Group delay, 85–86 Group velocity, 62 GSM, 278, 282 h parameters, 51, 74, 132, 197, 292 HALO, 283 Harmonic generators, see Multiplier(s) Hybrid coupler, 118

Ideal transformer, 46-47, 105, 306 Image frequency, 224, 244-245 Image impedance, 54-57, 59 Image propagation constant, 57-58 Impedance match(ing), 36, 95, 141 Impedance parameters, see z parameters Impedance transformation, 105, 121 Impedance transformer, 120 IMSUP, 240, 319, 321 IMT-2000, 279 Indefinite admittance matrix, 78-79, 207, 298 Indefinite scattering matrix, 80, 82 Inductor(s) circular spiral, 26 ferrite(s), 22-23 microstrip, 26 monolithic, 26 proximity effect, 22 self resonance, 21 spiral, 26-28, 30, 286 loss, 20, 22 Information, 1, 3-7 Injection locking range, 216 Input intercept point, 227 Insertion gain, 122 INTEL-SAT, 283

Intercept point input, 227, 242 output, 227 Third-order, 242, 281 Intermodulation distortion, 139, 191, 235 Third-order, 227, 241–242 Two-tone, 240 suppression, 230 Inverse Cheybyshev, 92–94 IP, 279 ISDN, 278 Isolation, 227–228, 235, 320–321

L circuit, 37–40 Ladder network(s), 88–89, 97 Laplace Transform, 255, 257 LMDS, 280 LO drive power, 227 Loop bandwidth, 250 Loop filter(s), 249–250, 254, 260–261, 264–265, 268–269, 276 Loop gain, 261–262, 265 Loss tangent, 16–17 Loss, conversion, 230

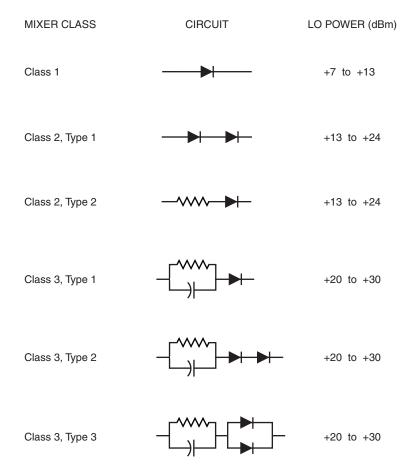

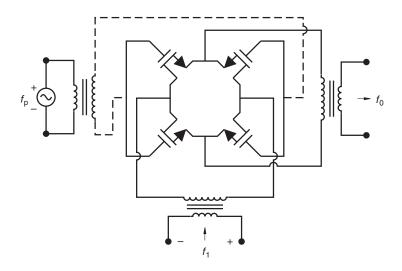

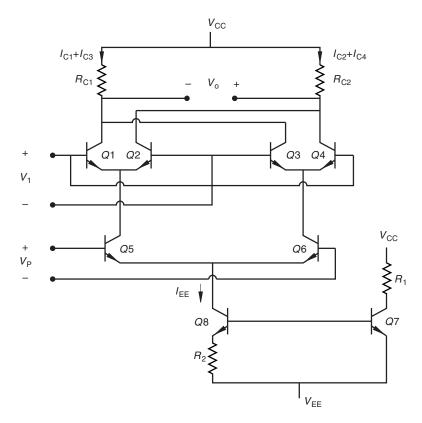

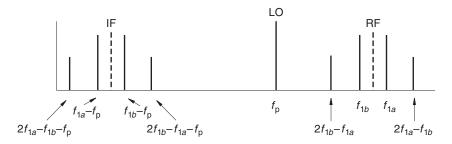

Manley-Rowe relations, 217 Mason's nontouching loop rules, 125 Maximum gain, 129 Maxwell equation(s), 66, 74 Microstrip, 26, 71–72, 115 MICSTP, 73 Minimum phase, 88–89 Minimum transconductance, 201 Mixer(s), 247 active, 235 class 1, 235 class 2, 235 class 3, 236 double-balanced, 227, 230, 232, 234-237, 274, 319 ring, 230-231 single balanced, 227-230, 232 single-ended, 227 star, 230-232 Modulation, 1 Modulator, 239 Multiplier(s), 216, 218, 247, 256 Gilbert cell, 236–240 MULTIPLY, 218–219

Nagaoka correction factor, 24 Natural frequency, 266–267, 269 Negative resistance, 204 NMT, 278 Noise figure, 122, 151–154, 157, 161-162, 164-165, 227, 243-244 double-sideband, 244, 246 single-sideband, 243-246 Noise measure, 152 Noise temperature, 151–152, 243–244 Noise, 1, 155, 191-192, 201, 204, 210, 230 flicker, 3, 144 Johnson, 144 minimum, 201, 203 Nyquist, 144 shot, 148-149 spot, 151 Nyquist formula, 147, 149, 151

Odd mode voltage, 28-29 Odd-mode current, 106-107 Ohmic contact, 13 Op-amp, see Operational amplifier(s) Open loop gain, 201, 262 Operational amplifier(s), 247-249, 254, 258-259, 262, 267, 272 Oscillator(s) Armstrong, 197–198 Clapp-Gouriet, 197-199 Colpitts, 197-200, 202 Hartley, 197-198, 202-203 injection-locked, 214 Pierce, 197-198 Vackar, 197-199 voltage controlled, 199, 206, 249-254, 256, 259-264, 270-272, 275

$\pi$  circuit, 39–41, 45 PACS, 279 Parallel plate line, 66 PARCONV, 292, 294 Phase detector(s), 247, 249, 250–254, 259-264, 271-272, 274-275 flip-flop, 272-273 sampling, 270-272 Phase error, 257-259 Phase margin, 247, 250 Phase velocity, 62 PLMR, 278 POLY, 97 Positive real, 96 Power amplifier(s), 3, 141, 191, 281 Power gain, 122

Probability, 6–7, 146 PSTN, 278

QPSK, 279, 281

Reflection coefficient, 62–63, 74–75, 77–78, 96–98, 114, 129, 204–205, 207–209, 296 Resistor diffused, 10 metal film, 11 Resonant frequency, 35–36, 37 Response time, 247, 250 Return loss, 114 Rollett criteria, 132

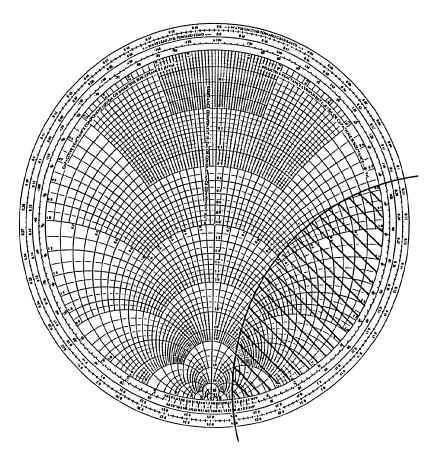

S parameter(s), 74, 77, 115, 124–126, 128-129, 132, 136, 138, 206-209, 292, 294-296, 298-299, 306-308 Saturated resistor, 14 Scattering matrix, *see S* parameter(s) Scattering parameters, *see S* parameter(s) Schottky barrier, 13, 222, 233 SDR, 279 Selectivity, 85 Series - series, 51, 52, 197 Series-shunt, 51-52 Shockley diode equation, 173 Shunt-series, 52-53 Shunt-shunt, 51, 200-201 Signal-to-noise ratio, 151, 243 Skin depth, 21-22Smith chart, 63-64, 131-133, 164 SOC, 283 SOLENOID, 23, 26, 285 Solenoid, 23, 285 parasitic capacitance, 25 Q, 25-26 SPARC, 209 Spectral regrowth, 281 Spurious voltages, 230 SSB, see Noise SSB, see Noise figure, single-sideband Stability, 122, 129-134, 136-138, 141, 198 amplifier, 205 factor, 206 Kurokawa, 213 oscillator, 210 temperature, 173 Sum frequency, 224

T circuit, 41-42, 45 **TACS**, 278 Tapped C, see Tapped capacitor Tapped capacitor, 42-45 TDMA, 3, 278, 280, 282 TDR, see Time domain reflectometer Telegrapher's equation(s), 59-61, 63, 65 - 66Temperature coefficient, 11, 74 Thompson-Bessel, 93, 96 Time domain reflectometer, 305-306, 308, 313 Transducer power gain, 89, 123–124, 126, 243 Transient(s), 204, 210, 247, 264 Transmission coefficient, 74, 77-78 Transmission line equation, 61, 63 Transmission line(s), 59-62, 65-66, 71, 106–116, 118–121, 132, 305, 310 Two-wire line, 65-66 Type 1 PLL, 254, 259, 262, 265, 267, 276 Type 2 PLL, 254, 262, 265, 267, 270, 275 Type 3 PLL, 262 UHF, 278 Unilateral amplifiers, 162, 164 approximation, 164 power gain, 126-127 Unloaded Q, 36 VCO, see Oscillator(s) Voltage coefficient, 11 Wilkinson divider, 120 y matrix, see y parameters y parameters, 51, 53, 74, 78, 132, 136-138, 197, 200, 207, 292, 294, 298 Y factor, 152–153 z parameters, 51-54, 56, 74, 123, 132, 197, 292, 294 16QAM, 281 1G, 282 2G, 282 3G, 279, 282 4G. 279 64QAM, 281

### WILEY SERIES IN MICROWAVE AND OPTICAL ENGINEERING

**KAI CHANG,** Editor *Texas A&M University*

FIBER-OPTIC COMMUNICATION SYSTEMS, Second Edition Govind P. Agrawal COHERENT OPTICAL COMMUNICATIONS SYSTEMS Silvello Betti, Giancarlo De Marchis and Eugenio Iannone HIGH-FREQUENCY ELECTROMAGNETIC TECHINQUES: RECENT ADVANCES AND **APPLICATIONS** Asoke K. Bhattacharyya COMPUTATIONAL METHODS FOR ELECTROMAGNETICS AND MICROWAVES Richard C. Booton, Jr. MICROWAVE RING CIRCUITS AND ANTENNAS Kai Chang MICROWAVE SOLID-STATE CIRCUITS AND APPLICATIONS Kai Chang RF AND MICROWAVE WIRELESS SYSTEMS Kai Chang DIODE LASERS AND PHOTONIC INTEGRATED CIRCUITS Larry Coldren and Scott Corzine MULTICONDUCTOR TRANSMISSION-LINE STRUCTURES: MODAL ANALYSIS TECHNIQUES J. A. Brandão Faria PHASED ARRAY-BASED SYSTEMS AND APPLICATIONS Nick Fourikis FUNDAMENTALS OF MICROWAVE TRANSMISSION LINES Jon C. Freeman OPTICAL SEMICONDUCTOR DEVICES Mitsuo Fukuda MICROSTRIP CIRCUITS Fred Gardiol HIGH-SPEED VLSI INTERCONNECTIONS: MODELING, ANALYSIS, AND SIMULATION A. K. Goel FUNDAMENTALS OF WAVELETS: THEORY, ALGORITHMS, AND APPLICATIONS Jaideva C. Goswami and Andrew K. Chan

ANALYSIS AND DESIGN OF INTERGRATED CIRCUIT ANTENNA MODULES K. C. Gupta and Peter S. Hall PHASED ARRAY ANTENNAS R. C. Hansen HIGH-FREQUENCY ANALOG INTEGRATED CIRCUIT DESIGN Ravender Goyal (ed.) MICROWAVE APPROACH TO HIGHLY IRREGULAR FIBER OPTICS Huang Hung-Chia NONLINEAR OPTICAL COMMUNICATION NETWORKS Eugenio Iannone, Franceso Matera, Antonio Mecozzi, and Marina Settembre FINITE ELEMENT SOFTWARE FOR MICROWAVE ENGINEERING Tatsuo Itoh, Giuseppe Pelosi and Peter P. Silvester (eds.) INFRARED TECHNOLOGY: APPLICATIONS TO ELECTRO-OPTICS, PHOTONIC DEVICES, AND SENSORS A. R. Jha SUPERCONDUCTOR TECHNOLOGY: APPLICATIONS TO MICROWAVE, ELECTRO-OPTICS, ELECTRICAL MACHINES, AND PROPULSION SYSTEMS A. R. Jha OPTICAL COMPUTING: AN INTRODUCTION M. A. Karim and A. S. S. Awwal INTRODUCTION TO ELECTROMAGNETIC AND MICROWAVE ENGINEERING Paul R. Karmel, Gabriel D. Colef, and Raymond L. Camisa MILLIMETER WAVE OPTICAL DIELECTRIC INTEGRATED GUIDES AND CIRCUITS Shiban K. Koul MICROWAVE DEVICES, CIRCUITS AND THEIR INTERACTION Charles A. Lee and G. Conrad Dalman ADVANCES IN MICROSTRIP AND PRINTED ANTENNAS Kai-Fong Lee and Wei Chen (eds.) OPTICAL FILTER DESIGN AND ANALYSIS: A SIGNAL PROCESSING APPROACH Christi K. Madsen and Jian H. Zhao OPTOELECTRONIC PACKAGING A. R. Mickelson, N. R. Basavanhally, and Y. C. Lee (eds.) **OPTICAL CHARACTER RECOGNITION** Shunji Mori, Hirobumi Nishida, and Hiromitsu Yamada ANTENNAS FOR RADAR AND COMMUNICATIONS: A POLARIMETRIC APPROACH Harold Mott INTEGRATED ACTIVE ANTENNAS AND SPATIAL POWER COMBINING Julio A. Navarro and Kai Chang ANALYSIS METHODS FOR RF, MICROWAVE, AND MILLIMETER-WAVE PLANAR TRANSMISSION LINE STRUCTURES Cam Nguyen FREQUENCY CONTROL OF SEMICONDUCTOR LASERS Motoichi Ohstu (ed.) SOLAR CELLS AND THEIR APPLICATIONS Larry D. Partain (ed.) ANALYSIS OF MULTICONDUCTOR TRANSMISSION LINES Clayton R. Paul

INTRODUCTION TO ELECTROMAGNETIC COMPATIBILITY Clayton R. Paul ELECTROMAGNETIC OPTIMIZATION BY GENETIC ALGORITHMS Yahya Rahmat-Samii and Eric Michielssen (eds.) INTRODUCTION TO HIGH-SPEED ELECTRONICS AND OPTOELECTRONICS Leonard M. Riaziat NEW FRONTIERS IN MEDICAL DEVICE TECHNOLOGY Arye Rosen and Harel Rosen (eds.) ELECTROMAGNETIC PROPAGATION IN MULTI-MODE RANDOM MEDIA Harrison E. Rowe ELECTROMAGNETIC PROPAGATION IN ONE-DIMENSIONAL RANDOM MEDIA Harrison E. Rowe NONLINEAR OPTICS E. G. Sauter ELECTROMAGNETIC FIELDS IN UNCONVENTIONAL MATERIALS AND STRUCTURES Onkar N. Singh and Akhlesh Lakhtakia (eds.) FUNDAMENTALS OF GLOBAL POSITIONING SYSTEM RECEIVERS: A SOFTWARE APPROACH James Bao-ven Tsui InP-BASED MATERIALS AND DEVICES: PHYSICS AND TECHNOLOGY Osamu Wada and Hideki Hasegawa (eds.) DESIGN OF NONPLANAR MICROSTRIP ANTENNAS AND TRANSMISSION LINES Kin-Lu Wong FREQUENCY SELECTIVE SURFACE AND GRID ARRAY T. K. Wu (ed.) ACTIVE AND QUASI-OPTICAL ARRAYS FOR SOLID-STATE POWER COMBINING Robert A. York and Zoya B. Popović (eds.) OPTICAL SIGNAL PROCESSING, COMPUTING AND NEURAL NETWORKS Francis T. S. Yu and Suganda Jutamulia SiGe, GaAs, AND InP HETEROJUNCTION BIPOLAR TRANSISTORS Jiann Yuan ELECTRODYNAMICS OF SOLIDS AND MICROWAVE SUPERCONDUCTIVITY Shu-Ang Zhou

# **Communication Channel**

#### 1.1 BASIC TRANSMITTER-RECEIVER CONFIGURATION

The design of radio frequency (RF) circuits borrows from methods used in lowfrequency audio circuits as well as from methods used in design of microwave circuits. Yet there are also important departures from these techniques, so the design of radio frequency circuits requires some specialized techniques not found in these other frequency ranges. The radio frequency range for present purposes will be taken to be somewhere between 300 MHz and 3 GHz. It is this frequency range where much of the present day activity in wireless communication occurs. In this range of frequency response of circuit elements that from the point of view of lumped, low-frequency analysis might be expected to be independent of frequency. At the same time the use of common microwave circuit elements such as quarter wave transformers is impractical because of the long line lengths required. The use of monolithic circuits have enabled many highfrequency designs to be implemented with lumped elements, yet the frequency response of these "lumped" elements still must be carefully considered.

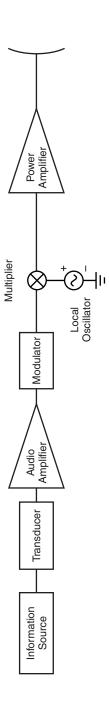

Today RF and digital designs have begun to move closer together, so typical communication systems incorporate both of these disciplines in their design. While direct digitizing of RF signals remains a challenge, there are many systems where digital signal processing is playing a larger role than ever in communication systems. A typical radio analog transmitter and receiver is shown in Fig. 1.1. In this system the information source could be an audio or video signal. This information in the process of being converted from, say, sound to an electrical signal by a transducer produces a very low voltage that must be amplified by an audio amplifier.

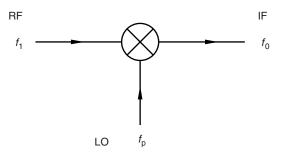

The modulator is shown schematically as a mixer that represents a wide variety of different modulation schemes. The two major categories are analog and digital modulation. In either case the modulator performs two functions. The first function is that it encodes the message in a certain way so as to meet the communication channel requirements for cost, noise immunity, fading, available

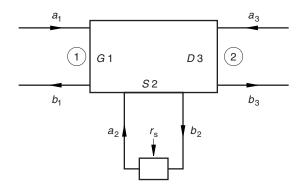

FIGURE 1.1 Diagram of a communication transmitter and receiver.

bandwidth, bandwidth efficiency (the ratio of the throughput data rate per Hertz in a given bandwidth), power efficiency (which measures the ability of a system to preserve the message under low power conditions), and so on.

For the amplitude modulation (AM) case, the mixer is a multiplier that multiples the information message with the local oscillator frequency. Just as the product of two sine waves produces sum and difference frequencies, so the message frequency is added to the local oscillator frequency. This produces two effects necessary for practical wireless communications. The first is that this enables forming multiple channels, which in the amplitude and frequency modulation (FM) analog systems are separated by different frequency bands. Otherwise, there would be massive interference between different signals. This method of separating signals is called frequency division multiple access (FDMA). Alternate methods are time division multiple access (TDMA) where two or more signals may share the same frequency band but use it at different times. The human receiver is able to integrate over the different time slots so that the message is perceived to be continuous. A third method is the spread spectrum technique known as code division multiple access (CDMA) where a broad bandwidth is used by multiple users continuously. However, each user sends and receives data that is coded in a particular way, different from all the other users. When there is interference between users, it is perceived as low-level noise.

The second function of the modulator is that it translates the message information to a much higher RF signal. For this reason antennas can be made a manageable size, with their mechanical size normally correspondings to the wavelength. A great deal of effort has gone into making smaller antennas, but there are always design compromises.

The final stage of the transmitter before reaching the antenna is the power amplifier. Since this component uses the greatest amount of power, high efficiency becomes an important factor. In FM systems, class C amplifiers are often used because, in practice, they can produce efficiencies as high as 70%. For AM systems, class A or AB amplifiers are often used because of the required linearity of AM signal transmission. However, class A amplifiers typically have efficiencies of 30% to 40%.

As for the receiver, the received signal is sometimes strong enough to be put directly into the mixer. However, as will be seen later (in Chapter 8), the overall noise response of the amplifier is greatly enhanced by using a low-noise amplifier for the front end. The demodulator in the receiver must correspond to the modulator in the transmitter. The subsequent intermediate frequency (IF) amplifier includes the required filtering to provide the desired selectivity for the received signal. The IF frequency is chosen to be sufficiently high to avoid most of the 1/f noise (f = frequency) or flicker noise. Since this circuit operates at a fixed frequency, it can be carefully tuned for optimum performance.

#### 1.2 INFORMATION AND CAPACITY

RF communication systems provide a means of carrying information from the transmitter to the receiver. Now, what exactly is information? *Webster's*  *Dictionary* states that "information" is "knowledge communicated or received concerning a particular fact or circumstance...." A narrower, technical definition that more closely aligns with our focus that "information" is an "indication of the number of possible choices of messages, which are expressible as the value of some monotonic function of the number of choices, usually log to the base 2." "Information" then is a term for data that can be coded for digital processing.

Some examples of data that illustrate the meaning of information is helpful. If a signal were sent through a communication channel that never changed, then it would be conveying no information. There must be change to convey a message. If the signal consisted of  $1 \ 0 \ 1 \ 0 \ 1 \ 0 \ 1 \ 0 \ \dots$ , there would be changes in the signal but still no information is conveyed, because the next bit would be perfectly predictable. So while change is important, it is not the sole criterion for information. There is one last example. If a signal in an amplitude modulation system consists of purely random voltage fluctuations, then again no information can be transmitted. It is simply noise, and the receiver becomes no more knowledgeable upon having heard it.

A communication system consists of a transmitter, a receiver, and a channel. The channel is capable of carrying only a certain limited amount of information. Roughly analogous to an information channel is a water pipe which, because of its diameter, is restricted to carrying only a certain amount of water. This limitation is given the technical term "capacity." It refers to the amount of information that is transmitted over a time interval of T seconds. The time interval can be broken up into shorter time intervals, each of duration  $\tau$ . Clearly, the more distinct time intervals  $\tau$  these are in the total time span T, the more information can be transmitted. The minimum size of  $\tau$  is determined by how well one pulse in one time frame can be distinguished from a pulse in a neighboring time frame. The limitation on how short a time frame can be is related to the channel bandwidth.

In addition the signal voltage will have a maximum amplitude that is limited by the available power in the system. This voltage range can be divided into many levels, each level representing a bit of information that is distinguished from another bit. The voltage range cannot be infinitely split because of the noise that is always present in the system. Clearly, the more voltage intervals there are in a given time frame  $\tau$ , the more information capacity there is in the system. Just as the flow of water through a pipe is limited by the amount of pressure on the water, by the friction on the walls of the pipe, and by the diameter of the pipe, so the capacity of a transmission system is limited by the maximum voltage level, by the noise in the system that tends to muddle the distinction between one voltage level and another, and by the bandwidth of the channel, which is related to the rise time of a pulse in the system.

In one of the time intervals,  $\tau$ , there are *n* voltage levels. The smaller that  $\tau$  is and the larger that *n* is, the more information there can be transmitted through the channel. In each time interval there are *n* possible voltage levels. In the next time interval there are also *n* possible voltage levels. It is assumed that the voltage

level in each time frame is independent of what is going on in other time frames. The amount of information transmitted in a total of T seconds corresponds to the product of the possible levels in each interval:

$$n \cdot n \cdot n \cdot n \dots n^{T/\tau} \tag{1.1}$$

The total information transmitted intuitively is directly proportional to the total time span T, which is defined as the log of the above product. By convention, the base-2 logarithm is used.

$$H = \frac{T}{\tau} \log_2 n \tag{1.2}$$

The system's capacity is simply the maximum *rate* of transmission (in bits/s) through a system:

$$C = \frac{H}{T} = \frac{1}{\tau} \log_2 n \tag{1.3}$$

System capacity is inversely proportional to the minimum time interval over which a unit of information can be transmitted,  $\tau$ . Furthermore, as the number of voltage levels increases, so does the capacity for more information.

Information can be transmitted through a channel in a variety of different forms, all producing the same amount of information. For example, suppose that a signal can take on any one of eight different voltage levels, 0, 1, ..., 7, in a given time interval  $\tau$ . But the eight signal levels could also equally be sent with just two levels, 0, 1. For every interval that has eight possible levels, three intervals will be needed for the two-level signal. A convenient conversion between the two systems is shown in Table 1.1.

Clearly, a 16-level signal could be transmitted by a sequence of four binary signals, and a 32-level signal with a sequence of five binary signals, and so on. For n levels,  $\log_2 n$  bits are needed. The information content of a signal is defined then to be the number of binary choices, or bits, that are needed

| I wo-Level Systems |       |  |

|--------------------|-------|--|

| n = 8              | n = 2 |  |

| 0                  | 000   |  |

| 1                  | 001   |  |

| 2                  | 010   |  |

| 3                  | 011   |  |

| 4                  | 100   |  |

| 5                  | 101   |  |

| 6                  | 110   |  |

| 7                  | 111   |  |

|                    |       |  |

| TABLE 1.1 | Eight-Level | and |

|-----------|-------------|-----|

| Two-Level | Systems     |     |

for transmission. A system is designed to transmit speech must be designed to have the capacity to transmit the information contained in the speech. While speech is not entirely what humans communicate, in a communication system it is what engineers have to work with. A decision must be made as to with what fidelity the speech is to be transmitted. This translates to the bandwidth requirement of an analog system, or the number of voltage levels available in a given total voltage range. Ultimately this restriction is always present even if sophisticated coding techniques are used. The capacity of the system must be  $\geq$ , the rate of information that is to be transmitted. Beyond this capacity, system cost, power levels, and available transmission media must be considered.

#### **1.3 DEPENDENT STATES**

The definitions of the preceding section imply that the voltage level in each time interval,  $\tau$ , is independent of the voltage level in other time intervals. However, one simple example where this is not the case is the transmission of the English language. It is known that in the English language the letter *e* appears more frequently than the letter *z*. It is almost certain that the letter *q* will be followed by the letter *u*. So, in transmitting a typical message in English, less information is actually sent than would be sent if every letter in the alphabet were equally likely to occur. A way to express this situation is in terms of probability. We are interested in the total number of signal combinations that could occur in a message *T* seconds long if each interval that is independent from the others is  $n^T/\tau$ . On average, every possible message *T* seconds long would have a probability of occurrence of  $1/n^{T/\tau}$ .

The probability takes the form

$$P = \frac{\text{number of occurrences of a particular event}}{\text{total number of events}}$$

(1.4)

For information measured in terms of probability, P = 1/n if there are *n* events specified as *n* voltage levels and each of these events is equally likely. For any one event, the information transmitted is written  $H_1 = -\log_2 P$ . For *m* intervals, each  $\tau$  seconds long, there will be *m* times more information. So for *m* intervals, the information written in terms of probability is

$$H = \frac{T}{\tau} \log_2 n = -m \log_2 P \quad \text{bits} \tag{1.5}$$

Consider a binary system where a number 0 occurs with probability p and the number 1 occurs with probability q. Knowing that p + q = 1, the information content of a message consisting of 0's and 1's is to be found. The total information is the sum of the information carried by the 0's and that of the 1's:

$$H = -\frac{T}{\tau}(p \cdot \log_2 p + q \cdot \log_2 q) \quad \text{bits} \tag{1.6}$$

If the probabilities of p and q are each 0.5, then the total information in T seconds is  $T/\tau$ . If, for example, p = 0.25 and q = 0.75, then

$$H = -\frac{T}{\tau} (0.25 \cdot \log_2 0.25 + 0.75 \cdot \log_2 0.75) \text{ bits}$$

$$H = \frac{T}{\tau} (0.5 + 0.3113) = 0.8113 \frac{T}{\tau} \text{ bits}$$

(1.7)

Hence, when there is a greater probability that an expected event will occur, there is less information. As p approaches 1 and q approaches 0, the near certainty of event with probability p will give 0 information. The maximum information occurs when p = q = 0.5.

This scenario can be generalized for *n* signal levels in a given signal interval  $\tau$ . Assume that each of these *n* signal levels,  $s_i$ , has a probability of occurrence of  $P_i$  where

$$P_1 + P_2 + \dots + P_n = \sum P_i = 1$$

(1.8)

Assume further that the probability of a finding a given signal level is independent of the value of the adjacent signal levels. The total information in  $T/\tau$  intervals or in T seconds is

$$H = -\frac{T}{\tau} \sum_{i}^{n} P_i \log_2 P_i \quad \text{bits}$$

(1.9)

The capacity required to transmit this amount of information is then

$$C = -\frac{1}{\tau} \sum_{i}^{n} P_i \log_2 P_i \quad \text{bits/s} \tag{1.10}$$

In the case where each level is equally likely,  $P_1 = P_2 = P_3 = \cdots P_n = 1/n$ , then for the *n* level signal,

$$H = -\frac{T}{\tau} \sum_{i}^{n} P_i \log_2 P_i = \frac{T}{\tau} \log_2 n \quad \text{bits}$$

(1.11)

More detail on information transmission can be found in specialized texts; a short introduction is given by Schwartz [1]. In general, this study of radio frequency design, the primary focus will be on fundamental hardware design used in transmitters and receivers. Other topics that are of great interest to communication engineers such as programming digital signal processing chips, modulation schemes, and electromagnetic propagation problems are more fully explored in

#### 8 COMMUNICATION CHANNEL

specialized texts in those areas. In this book these areas will be referred to only as needed in illustrations of how systems can be implemented.

#### PROBLEMS

- **1.1** A pulse train is being transmitted through a channel at the maximum channel capacity of  $25 \cdot 10^3$  bits/s. The pulse train has 16 levels.

- (a) What is the pulse width?

- (b) The pulse width is doubled and sent back on the same channel. What is number of levels required?

#### REFERENCES

1. M. Schwartz, *Information Transmission, Modulation, and Noise*, 3rd ed., New York: McGraw-Hill, 1980, Ch. 1.

# Resistors, Capacitors, and Inductors

### 2.1 INTRODUCTION

At radio frequencies passive circuit elements must be considered more carefully than in lower-frequency designs. The simple resistor, capacitor, or inductor cannot be counted on to provide pure resistance, capacitance, or inductance in high-frequency circuits. Usually the "lumped" element is best modeled as a combination of these pure elements. In addition, when the size of the element becomes larger than 0.1 wavelength in the circuit medium, the equivalent circuit should include the transmission lines.

### 2.2 **RESISTORS**

Integrated circuit resistors can be classified into three groups: (1) semiconductor films, (2) deposited metal films, and (3) cermets (a mixture of metal and dielectric materials). Of these, only the first two have found widespread use in high-frequency circuits. Semiconductor films can be fabricated by diffusion into a host semi-insulating substrate, by depositing a polysilcon layer, or by ion implantation of impurities into a prescribed region. Polysilcon, or polycrystalline silicon, consists of many small submicron crystals of silicone with random orientations.

### 2.2.1 Resistor Types

The resistance value of an integrated circuit resistor depends on the conductivity of the channel through which the current is flowing. In the diffused resistors in a semiconductor substrate, the conductivity is a function of the doping concentration and the carrier mobility. The conductivity is

$$\sigma = q(\mu_n n + \mu_p p) \tag{2.1}$$

It is usually expressed in the units of  $(\Omega - \text{cm})^{-1}$ . In this expression, q is the electronic charge  $(1.602 \cdot 10^{-19} \text{ C})$ ,  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities  $(\text{cm}^2/\text{V} - \text{s})$ , and n and p are the number of free electrons and holes, respectively, that are available for conduction  $(\text{cm}^{-3})$ . At room temperature it may be assumed that all the impurity atoms in the semiconductor are ionized. This means that for an *n*-type semiconductor, the number of available electrons is equal to the donor impurity concentration:

$$n_n \approx N_{\rm D}$$

(2.2)

Similarly, for a *p*-type semiconductor, the number of holes equals the acceptor impurity concentration:

$$p_p \approx N_{\rm A}$$

(2.3)

In either an n-type or a p-type semiconductor, the relationship between the electron and hole concentrations is

$$n p = n_i^2 \tag{2.4}$$

where  $n_i = 1.45 \cdot 10^{10}$  cm<sup>-3</sup> for silicon and  $9.0 \cdot 10^6$  for gallium arsenide. This is called the *mass action law*. Thus, for an *n*-type semiconductor, the conductivity is

$$\sigma = q \left( \mu_n N_{\rm D} + \mu_p \frac{n_i^2}{N_{\rm D}} \right) \approx q \mu_n N_{\rm D}$$

(2.5)

Typically, in integrated circuits, n-channel FETs and NPN bipolar transistors are preferred because of the much larger electron mobility over that of the hole mobility. The total number of processing steps required in a circuit design often dictates the choice of resistor channel type.

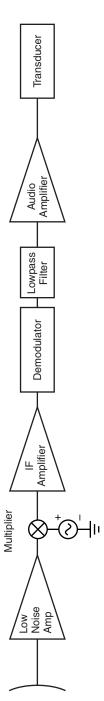

Ideally the diffused resistor with conductivity  $\sigma$  can be represented by the rectangular block shown in Fig. 2.1. The resistance of the rectangular block is

$$R = \frac{L}{\sigma WT}$$

(2.6)

It is often convenient to separate the "processing" aspects from the "layout" aspects of the resistor. This is done by defining the sheet resistance in  $(\Omega/\Box)$  as

$$R_{\Box} = \frac{1}{\sigma T} \tag{2.7}$$

so that the total resistance is

$$R = R_{\Box} \frac{L}{W} \tag{2.8}$$

The length to width ratio determines the resistance value once the conductivity and layer thickness is set.

FIGURE 2.1 Diffused resistor of length L, width W, height T.

| <b>TABLE 2.1</b> | Resistor | Materials |

|------------------|----------|-----------|

|------------------|----------|-----------|

| Resistor Type    | Resistance               | Temperature Coefficient | Voltage Coefficient |

|------------------|--------------------------|-------------------------|---------------------|

| Diffused Si      | 10 to 100 $\Omega/\Box$  | 1500 ppm/°C             | 200 ppm/V           |

| Diffused GaAs    | 300 to 400 $\Omega/\Box$ | 3000 to 3200 ppm/°C     |                     |

| Polysilcon       | 30 to 200 $\Omega/\Box$  | 1500 ppm/°C             | 100 ppm/V           |

| Ion implantation | 0.5 to 2 k $\Omega/\Box$ | 400 ppm/°C              | 800 ppm/V           |

| AuGeNi (Alloyed) | $2 \Omega/\Box$          |                         |                     |

| Thin film Cr     | 13 μΩ-cm                 | 3000 ppm/°C             | _                   |

| Thin film Ti     | 55 to 135 µΩ-cm          |                         | _                   |

| Thin film Ta     | 180 to 220 μΩ-cm         | _                       | _                   |

| Thin film TaN    | 280 μΩ-cm                | _                       | _                   |

| Thin film Ni     | 7 μΩ-cm                  | _                       | _                   |

| Thin film NiCr   | 60 to 600 μΩ-cm          | —                       | —                   |

Sources: Refs. [1-3].

Metal films are made by evaporation of the desired metal on substrate and the desired pattern determined by photo lithography. Metal films are generally superior to the semiconductor films in that metal films are less sensitive to changes in temperature and voltage. Table 2.1 shows some of the main properties of a variety of methods and materials. The temperature and voltage coefficients are measures of the percentage change in resistance as a function of a change in a given parameter. The definition of temperature coefficient is (dR/dT)/R and the voltage coefficient is (dR/dV)/R.

#### 2.2.2 Resistance Determination from Layout

The layout shape of a resistor is typically simply a straight rectangular bar, as shown in Fig. 2.1. However, it may at times be better to try different shapes

11

in order to optimize the overall layout of a circuit. A convenient method for determining the resistance between two points on any shape is the method of curvilinear squares. Of course computer-based numerical methods such as the finite-element technique, can also be used. However, using paper and pencil, in just 20 minutes an answer could be obtained to within 10% to 20% accuracy.

A curvilinear rectangle may be defined "as any area which is bounded on opposite sides by two flux lines, and on the other sides by two equipotential lines..." [4]. These rectangles can be divided and subdivided into squares of ever-decreasing size. Then, based on Eq. (2.8), the total resistance can be found by counting the squares.

Rather than estimating the "squareness" of a curvilinear square, circles can be drawn between two flow lines using a compass or a template. Each curvilinear square should have its four sides tangent to the inscribed circle.

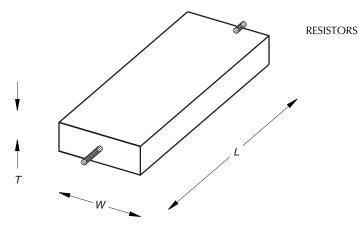

The curvilinear square method is illustrated in Fig. 2.2. The procedure takes the following form:

1. Draw flow lines between the two electrodes as if water is to travel between the electrodes in a laminar flow. The spacing between the two flow lines is less important than the shape of the flow lines. The flow lines should intersect the electrodes at right angles.

**FIGURE 2.2** (a) Resistor shape with a flow line; (b) addition of tangential circles; (c) drawing best-fit curvilinear squares; (d) expansion of the fractional curvilinear square from (c).

- 2. Between two adjacent flow lines, draw a series of circles tangent to the flow lines and to each other.

- 3. Draw equipotential lines between the circles orthogonal to the flow lines.

- 4. If there is more rectangle left over than the number of circles, fill the remaining part of the rectangle with circles in the orthogonal direction. Continue this until the last rectangle is sufficiently close to becoming a square.

- 5. Starting with the smallest square, count all the squares in series. Invert and add to the next largest row of squares going in the orthogonal direction. Continue inverting and adding to the next larger row of squares.

As Fig. 2.2 shows, the first step, in which the smallest squares are added, has the result 2. Step 2 consists in inverting the result of step 1 and adding the remaining series of squares, with the result  $\frac{1}{2} + 1 = 1.5$ . In step 3 the result of step 2 is inverted and added to the remaining series of squares. At the end of this step, the result is (1/1.5) + 2 = 2.67. Finally step 4 gives (1/2.67) + 5 = 5.375. The resistance then in the indicated section of the resistor is  $5.375 \cdot R_{\Box}$ . These steps are repeated for the other parallel sections to obtain the total resistance as a parallel combination.

The obvious application of this method to electrical engineers is in finding the resistance of an arbitrarily shaped resistor. However, it can also be applied in finding the magnetic reluctance in a magnetic circuit, capacitance, heat convection, and, of course, laminar fluid flow.

There are a couple of other details that should be considered in predicting resistance values. One is that the rectangular bars of resistance are not really rectangular bars. The bottom is rounded, and a better estimate can be found by taking this characterstic into account. Another complication is that somewhere a semiconductor diffused resistor is going to have to come in contact with a metal. The resulting Schottky barrier can cause an additional voltage drop. Normally an Ohmic contact is used for this interface. An Ohmic contact is formed by heavily doping the semiconductor at the point of contact with the metal. This essentially promotes tunneling of electrons through the barrier. Nevertheless, there is still some residual resistance from the contact. Consequently the previously given expression for resistance, Eq. (2.8), should be modified to incorporate the contact resistance,  $R_c$ :

$$R = R_{\Box} \frac{L}{W} + \frac{2R_c}{W}$$

(2.9)

A typical value for  $R_c$  is about 0.25  $\Omega$ -mm.

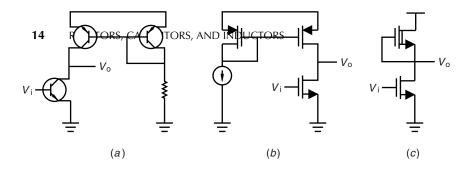

Active loads are often used in integrated circuits in place of passive loads where the required resistance value is fairly high. The primary advantage of the active load is its compact size relative to that of a large passive load. These are often used in common emitter NPN transistor amplifiers or FET amplifiers as shown in Fig. 2.3. As the figure shows, the base-collector, the gate-drain of the enhancement mode FET, and the gate-source of the depletion mode FET are

FIGURE 2.3 Active loads using (a) common emitter structure, (b) p-channel enhancement mode MOSEET load, and (c) n-channel depletion mode MOSEET load  $n^+$ (a) (b)

**FIGURE 2.4** Charge distribution for (*a*) shorted gate active load and (*b*) a saturated resistor.

shorted together. An active load can also be made in GaAs with a "saturated resistor" [5]. This structure is essentially a GaAs MESFET without a gate, and it is simpler to construct than the usual depletion mode FET with the gate shorted to the source. The saturation current in GaAs is reached at a rather low saturation field of 3 kV/cm. This means that once saturation has occurred, there is a small increase in the current with each increase in voltage. Consequently a large effective resistance is obtained. The saturated resistor channel depth is effectively greater than that of the MESFET channel as shown in Fig. 2.4. Consequently, for a given resistance value, the width of the saturated resistor would have to be made narrower. Resistance values of 8 to 10 k $\Omega$  have been obtained [5]. However, the simpler processing of the saturated resistor has given improved reliability and repeatability of these devices.

#### 2.3 CAPACITORS

Some of the most important parameters that need consideration in choosing a capacitance are (1) the capacitance value, (2) capacitance value tolerance, (3) loss or Q, (4) temperature stability, (5) mechanical packaging and size, and (6) parasitic inductance. These criteria are interdependent, so often the appropriate compromises depend on the constraints imposed by the particular application. This section will consider both hybrid and monolithic capacitor designs.

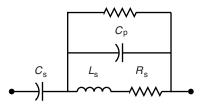

#### 2.3.1 Hybrid Capacitors

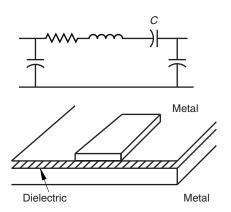

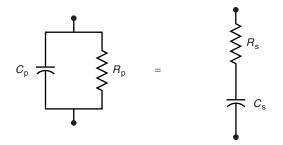

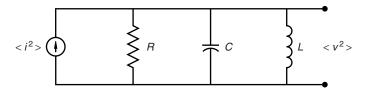

Hybrid capacitors are available in both single-layer capacitors for high-frequency low-capacitance applications and multi-layer capacitors for higher capacitance. Even for multilayer chip capacitors, the self-resonant frequency for a 0.1 pF capacitor is over 10 GHz and for a 1000 pF capacitor the self-resonant frequency of 250 MHz. These capacitors can be attached to hybrid circuit boards to provide high available capacitances with relatively low loss. Unlike low-frequency circuits, certain parasitic circuit elements must be accommodated in the overall design. The parasitic inductance is affected by the packaging, since it is usually associated with the lead attachments to the capacitor and line length effects inside the capacitor. In low-frequency circuits the effect of the inductance is so small that it can safely be neglected. However, at radio frequencies both the inductance and the metal losses often become significant. Consequently the equivalent circuit for a chip capacitor as developed by chip capacitor manufactures is shown in Fig. 2.5 and can sometimes be simplified as simply a series RLC circuit. The additional parallel resistance,  $R_{\rm p}$  is added to this equivalent circuit to model resistive losses caused by dielectric loss. This parameter is the main loss at low frequencies in the hertz to kilohertz range, but at RF it becomes negligible when compared to  $R_{\rm s}$ . The impedance of the circuit is

$$Z = R_{\rm s} + \frac{j}{\omega C} (\omega^2 L C - 1) \tag{2.10}$$

Consequently the effective capacitance is frequency dependent:

$$C_{\rm eff} = \frac{C}{1 - (\omega/\omega_0)^2}$$

(2.11)

where  $\omega_0 = 1/\sqrt{LC}$  is the self-resonant frequency.

While loss in capacitors is usually less than that in inductors, capacitor loss can still be significant in circuit performance. Loss can be described in terms of dissipation factor (DF), loss tangent  $(\tan \beta)$ , the equivalent series resistance  $(R_s)$ ,

FIGURE 2.5 Typical equivalent circuit for a chip capacitor.

and  $Q_{cap}$ . Since the circuit Q is assumed to result from a series RLC configuration,

$$R_{\rm s} = \frac{X_{\rm c}}{Q_{\rm cap}} \tag{2.12}$$

The loss terms then are related by

$$\tan \delta = \mathrm{DF} = \frac{1}{Q_{\mathrm{cap}}} \tag{2.13}$$

The angle  $\delta = 90^{\circ} - \theta$ , where  $\theta$  is the angle between the voltage and the current. In a lossless capacitor,  $\theta = 90^{\circ}$ .

In a capacitor the dielectric is the primary source of loss. An RF field can cause the dipole molecules in the dielectric to rotate at a rate proportional to the applied frequency and with a force proportional to electric field strength. The rotation of these molecular dipoles is converted to heat loss. When E is the electric field and f is the frequency, the energy dissipation is given by the following empirical expression [6]:

$$\mathcal{E} = E^2 f 55.5 \cdot 10^{-6} \varepsilon_r \tan \delta \quad \text{W/cm}^3 \tag{2.14}$$

Some of the most widely used dielectric materials for capacitors are shown in Table 2.2

The BaTiO<sub>3</sub>,  $\varepsilon_r = 8000$ , material provides the most compact capacitor. However, it has relatively poor temperature coefficient, tan  $\delta$  shift with voltage, coefficient of expansion in terms of temperature, piezoelectric effects, and aging qualities because of its porosity.

The BaTiO<sub>3</sub>,  $\varepsilon_r = 1200$ , capacitance varies by +15% from  $-55^{\circ}$ C to  $125^{\circ}$ C. When the BaTiO<sub>3</sub> materials are heated to about the Curie point, the value for  $\varepsilon_r$  jumps up about 10% to 15%. After cooling and waiting 10 hours, the dielectric constant drops back down only 3% of its peak value, and after 10,000 hours, it drops down only 7% of its peak value. As the voltage changes over a range of 30 V, the loss tangent increases from 0.01 to 0.1 at low frequencies. There are four crystalline phases for BaTiO<sub>3</sub> as it is heated up. The crystal changes from orthorhombic to tetragonal to cubic (which is near the Curie point). At each of

| Dielectric                                        | At Low Frequency | At 100 MHz | At 1 GHz |

|---------------------------------------------------|------------------|------------|----------|

| BaTiO <sub>3</sub> , $\varepsilon_{\rm r} = 8000$ | _                | 0.1        |          |

| BaTiO <sub>3</sub> , $\varepsilon_r = 1200$       | 0.01             | 0.03       | 0.10     |

| Ceramic (NPO), $\varepsilon_r = 30$               | 0.0001           | 0.002      | 0.10     |

| Alumina, $\varepsilon_r = 9.8$                    | _                | 0.0005     |          |

| Porcelain (ATC100), $\varepsilon_r = 15$          | —                | 0.00007    |          |

TABLE 2.2 Loss Tangent  $(\tan \delta)$  of Dielectric Materials

these changes, there is an abrupt change in the mechanical size of the crystal [7]. This has deleterious implications on solder joints of the capacitor.

The capacitance using NPO material varies with temperature  $\pm 30 \text{ ppm/}^{\circ}\text{C}$ . It moves in the negative direction, then in the positive direction exceeding the initial capacitance, and finally settling down near the original capacitance as the temperature rises. Hence it gets the name NPO.

The porcelain materials provide high Q, no piezoelectric effects, no aging effects (since it is not a porous material), and temperature coefficient of  $\pm$  30 ppm/°C up to 125°C. The coefficient of expansion of the porcelain capacitor is the same as alumina (Al<sub>2</sub>O<sub>3</sub>). For this reason, when mounted on an alumina substrate, the two will expand the same amount. The series resistance at 1 GHz varies with the value of capacitance as shown in Table 2.3.

For a 30-pF BaTiO<sub>3</sub>,  $\varepsilon_r = 1200$ , capacitor operating at 300 MHz, the resistance can be as high as 1  $\Omega$  and result in 0.3-to 3-dB dissipation loss. In solid state circuits that operate in high-current and low-voltage conditions, these losses can be quite significant. The generated heat further degrades the loss tangent, which increases the heat dissipation. Thermal runaway can occur, causing self-destruction. Of the materials shown in Table 2.2, porcelain provides the best loss tangent, especially at frequencies in the 1 to 3 GHz range.

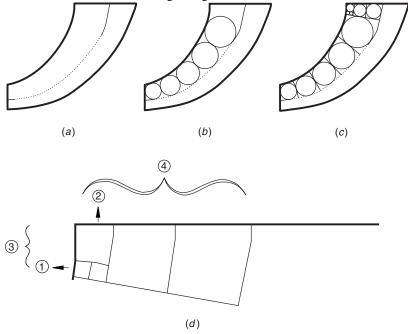

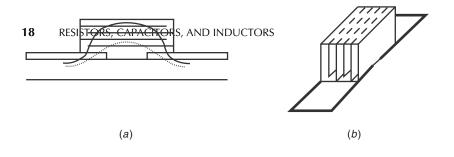

The frequency range of a chip capacitor can be extended by the simple expedient of turning it on its side (Fig. 2.6). Resonances appear to be the result of different path lengths of the path through the lower plates and upper plates of a multi-layer capacitor. Turning the capacitor on its side tends to equalize the path lengths and eliminates all odd-order harmonic resonances [7].

#### 2.3.2 Monolithic Capacitors

Capacitors in monolithic circuits are best avoided where possible because of the amount of real estate they occupy. Nevertheless, they are sometimes required. The capacitance tolerance is typically  $\pm 10\%$ , and capacitance values range from 0.2 to 100 pF. There are four types of monolithic capacitors that might be used in

TABLE 2.3 Resistance of

| Porcelain Capacitors |                     |

|----------------------|---------------------|

| <i>C</i> , pF        | $R_{\rm s}, \Omega$ |

| 5.6                  | 0.38                |

| 10                   | 0.27                |

| 20                   | 0.19                |

| 30                   | 0.16                |

| 40                   | 0.13                |

| 50                   | 0.12                |

| 100                  | 0.088               |

Source: Ref. [7].

FIGURE 2.6 Metallic conductors in (a) horizontal and (b) vertical orientation.

monolithic circuit designs: (1) open circuit stub, (2) interdigital line, (3) metalinsulator metal, and (4) varactor diode.

The open circuit stub capacitance is simply an open circuit transmission line whose length is  $< \lambda/4$ . The capacitive susceptance is obtained from the transmission line equation:

$$B = Y_0 \tan\left(\frac{\omega l}{v_c}\right) \tag{2.15}$$

The value of the susceptance depends on the characteristic admittance,  $Y_0$ , of the transmission line, the length, l, of the transmission line, and the substrate material that governs the velocity of the wave,  $v_c$ . This open circuit stub provides a shunt capacitance to ground. While the susceptance is not proportional to  $\omega$  as in lumped capacitors, it is a good approximation when the argument of the tangent function is small. Line lengths can use a large amount of real estate at low frequencies, so typically the open stub capacitor is most useful at frequencies greater than about 8 GHz.

The interdigital capacitor shown in Fig. 2.7, unlike the open stub, provides series capacitance. It is most useful for capacitances less than 1 pF, and at 12 to 14 GHz it typically has a Q of 35 to 50. The equivalent circuit shown in Fig. 2.7 includes series resistance and inductance, as well as some shunt capacitance to ground. The latter is caused by the metal-insulator-ground metal of the microstrip structure. The main series capacitance can be estimated from

$$C = (N_{\rm f} - 1)C_{\rm g}\ell \tag{2.16}$$

where  $N_{\rm f}$  is the number of fingers,  $\ell$  is the finger length, and  $C_{\rm g}$  is the static gap capacitance between the fingers.

A third type of capacitor is the metal-insulator-metal capacitor (Fig. 2.8). Of the four monolithic capacitors, this is the most popular and is the most obvious. The dielectric thickness typically used is 0.1 to 0.4  $\mu$ m. Losses can be reduced if the metal thickness is greater than two skin depths. The metal surface roughness should be as smooth as possible to reduce losses and avoid pin holes in the dielectric. Typically the capacitance ranges from 50 to 300 pF/mm<sup>2</sup> [2]. When

FIGURE 2.7 Interdigital capacitor layout and equivalent circuit.

FIGURE 2.8 Metal-insulator-metal capacitor and equivalent circuit.

the conductor losses prevail over the dielectric losses, the conductor quality factor is [1]

$$Q_{\rm c} = \frac{3}{2\omega R_{\rm s}(C/A)l^2} \tag{2.17}$$

In this expression  $R_s$  is the surface skin resistivity, C is the capacitance, A is the plate area, and l is length of the plate in the direction the microwave current enters the plate. If the dielectric quality factor is

$$Q_{\rm d} = \frac{1}{\tan \delta} \tag{2.18}$$

then the total Q is

$$\frac{1}{Q_{\rm T}} = \frac{1}{Q_{\rm d}} + \frac{1}{Q_{\rm c}}$$

(2.19)

| Dielectric        | Nominal $\varepsilon_r$ | Range of $\varepsilon_r$ | Temperature<br>Coefficient ppm/°C |

|-------------------|-------------------------|--------------------------|-----------------------------------|

| SiO <sub>2</sub>  | 5                       | 4-5                      | 50-100                            |

| SiN               | 7.5                     | 5.5-7.5                  | 25-35                             |

| Ta <sub>2</sub> O | 21                      | 20-25                    | 200-400                           |

| $Al_2O_3$         | 9                       | 6-10                     | 100-500                           |

| Polyimide         | 3.5                     | 3-4.5                    | -500                              |

|                   |                         |                          |                                   |

TABLE 2.4 Monolithic Capacitor Dielectric Materials

Source: Ref. [1].

The dielectric films used in monolithic capacitors tend to be much higher than that obtained in the hybrid capacitors described above. Some typical metalinsulator-metal dielectric materials are shown in Table 2.4. The variableness in the dielectric constant is a result of the variation in deposition methods, uniformity, and thickness.

The fourth way of obtaining capacitance is by means of the junction capacitance of a Schottky diode. This capacitance is

$$C = \frac{C_0}{(1 - V/\phi)^{\gamma}}$$

(2.20)

where  $\gamma \approx 1/2$  [8, p. 190]. When the applied voltage, V, is zero, the capacitance is  $C_0$ . A major disadvantage of this capacitance is its voltage dependence relative to the built-in potential,  $\phi$ .

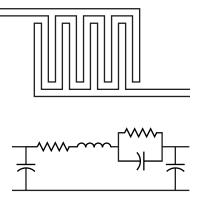

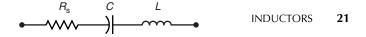

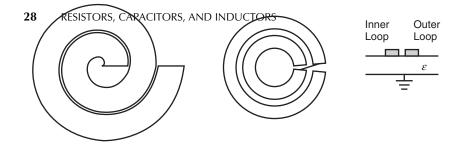

## 2.4 INDUCTORS

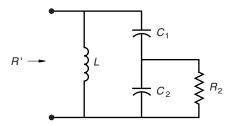

Inductors operating at radio frequencies have a variety of practical limitations that require special attention. A tightly wound coil in addition to providing a self inductance also has heat loss due to the nonzero wire resistance, skin effect losses, eddy current losses, and hysteresis losses when a magnetic material is used. Furthermore two conductors close together at two different voltages will also exhibit an interelectrode capacitance. At radio frequencies these effects cannot be neglected as easily as they could at lower frequencies. The equivalent circuit is shown in Fig. 2.9. In this figure the series resistance,  $R_s$ , represents the conductor loss as well as the skin effect losses. The parallel resistance,  $R_p$ , represents the effect of eddy current losses and the hysteresis loss in magnetic materials when present. The shunt capacitance, C, is the capacitance found between the coils. Straightforward circuit analysis gives the impedance for this equivalent circuit:

$$Z = \frac{R_{\rm p}R_{\rm s} + R_{\rm p}L_{\rm s}}{s^2 L C R_{\rm p} + s (R_{\rm s} C R_{\rm p} + L) + R_{\rm s} R_{\rm p}}$$

(2.21)

FIGURE 2.9 Simple equivalent circuit for an inductor.

If  $R_p$  is considered so large as to have negligible effect, and if the remaining series circuit  $Q = 1/\omega R_s C$  is large, then the effective inductance is approximately

$$L_{\rm eff} = \frac{L}{1 - \omega^2 LC} \tag{2.22}$$

and the effective resistance is

$$R_{\rm eff} = \frac{R_{\rm s}}{1 - \omega^2 LC} \tag{2.23}$$

Clearly, the presence of the capacitance dramatically increases the effective inductance and capacitance near the self-resonant frequency of the inductor. The self-capacitance of the inductor is a function of the coil length to coil diameter ratio,  $\ell/D$ , and it has an optimum value [9,10]. The following sections will describe in greater detail the origin of the parasitic circuit elements for a practical RF inductor and some design methods for RF inductors.

#### 2.4.1 Resistance Losses

The dc current flowing through a wire with a cross-sectional area, *A*, will encounter twice the resistance if the area is doubled. At radio frequencies the ac current tends to flow near the surface of the conductor because of the skin effect. This can be illustrated by an electric field impinging on a conductor whose resistance is not zero. The field will penetrate into the conductor and will exponentially decay as it penetrates deeper:

$$E(x) = E_0 e^{-x/\delta} \tag{2.24}$$

where

$$\delta = \sqrt{\frac{\rho}{\pi f \,\mu}} \tag{2.25}$$

In this equation f is the frequency,  $\rho$  is the resistivity, and  $\mu$  is the permeability. Because of this skin depth, the resistance of a given wire with radius R will have a higher resistance at high frequencies than at dc. The ac resistance is given by [9]

$$R_{\rm AC} = \frac{A_{\rm tot}}{A_{\rm skin}} R_{\rm dc}$$

| Metal    | Conductivity $(\Omega$ -cm) <sup>-1</sup> | Skin Depth<br>(cm)    |

|----------|-------------------------------------------|-----------------------|

| Brass    | $1.57 \cdot 10^5$                         | $12.7 \cdot f^{-1/2}$ |

| Aluminum | $3.54 \cdot 10^{5}$                       | $8.46 \cdot f^{-1/2}$ |

| Gold     | $4.27 \cdot 10^{5}$                       | $7.7 \cdot f^{-1/2}$  |

| Copper   | $5.8 \cdot 10^5$                          | $6.61 \cdot f^{-1/2}$ |

| Silver   | $6.14 \cdot 10^{5}$                       | $6.61 \cdot f^{-1/2}$ |

| Mu-metal | $1.58 \cdot 10^8$                         | $0.4 \cdot f^{-1/2}$  |

TABLE 2.5 Common Conductors

$$= \frac{\pi R^2}{\pi R^2 - \pi (R - \delta)^2} R_{\rm dc}$$

$$= \left[ \frac{\pi R^2}{2\pi \delta R - \pi \delta^2} \right] R_{\rm dc}$$

(2.26)

At high frequencies

$$R_{\rm ac} \approx \frac{R}{2\delta} R_{\rm dc}.$$

(2.27)

The possibility for  $R_{ac}$  to be infinite or even negative clearly indicates that Eq. (2.26) has gone beyond its range of applicability. The problem is that the skin depth has become greater than twice the wire radius. Listed in Table 2.5 are the resistivities and skin depths of a few common metals.

Another important loss mechanism is called the *proximity effect*. When one conductor supporting a changing magnetic field is brought close to another conductor, currents will be induced on the second conductor in conformity with Faraday's law. These currents are called *eddy currents*, and they flow in closed paths so as to produce a magnetic field that is in opposition to the originally applied external field. These currents produce *Joule heating*. This is exactly the condition that occurs in a tightly wound inductive coil. When many wires are close together, the loss problem is compounded, and the eddy current losses can be quite significant. As an illustration of this, consider a coil with length to diameter ratio of 0.7. If this coil is unwound and laid out as a straight wire, the losses will drop by a factor of 6 [9, p. 47].

#### 2.4.2 Magnetic Materials

A recurring problem is the need for a large value of inductance. An obvious solution is to increase the flux density within an inductor coil with the addition of a magnetic material with high permeability  $\mu_r$ . Most magnetic materials introduce losses that are unacceptable at radio frequencies. A variety of ferrite materials however have been found to have low loss at radio and microwave frequencies in comparison with most other magnetic materials. The relative permeability for

ferrites is in the range  $10 < \mu_r < 150$ . Above the cutoff frequency,  $\mu_r$  drops off quickly. The higher the permeability, the lower the cutoff frequency. Typically, for  $\mu_r = 10$ ,  $f_{cutoff} = 1$  GHz. For  $\mu_r = 150$ ,  $f_{cutoff} = 20$  MHz.

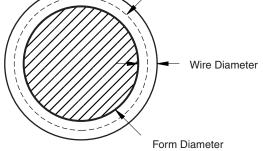

## 2.4.3 Solenoid Design up to 2 GHz [11]<sup>+</sup>

A design procedure for a single layer solenoid is given below. The computer program, SOLENOID, follows the procedure outlined here and is described in Appendix A. The given parameters for the analysis of a solenoid are the form length, number of turns (n), and the form diameter. The pitch is defined as

$$Pitch = \frac{form \ length}{n} \quad inches \tag{2.28}$$

For maximum Q, the wire diameter should be 0.6 to  $0.7 \cdot \text{pitch}$ . The wire diameter is selected from the standard wire sizes. For a given American wire gauge (AWG), the wire diameter is

Wire diameter =

$$\frac{0.005}{92^{(AWG-36)/39}}$$

inches (2.29)

Another parameter is the turn diameter. It represents the diameter where the magnetic flux is generated. As shown in Fig. 2.10, it is merely (turn diameter) = (form diameter) + (wire diameter). With these quantities now defined, the analysis recipe can be followed.

$$x = \frac{\text{turn diameter}}{\text{form length}}$$

(2.30)

$$K_n = \frac{1}{1 + 0.45 \text{Wrn} - 10000059r^2}$$

(2.31)

FIGURE 2.10 Inductor form cross section.

† Reprinted with permission, Microwave Journal, Vol 39, pp. 70-76.

When the wire diameter = 0, the current sheet correction factor, *s*, is set to 1. When the wire diameter > 0, the *s* correction factor is needed. The *s* factor, and finally the inductance, is found by first finding *a* and *b* as shown below:

$$a = 2.3 \cdot \log_{10} \left( 1.73 \cdot \frac{\text{wire diameter}}{\text{pitch}} \right)$$

(2.32)

$$b = 0.336 \left( 1 - \frac{2.5}{n} + \frac{3.8}{n^2} \right)$$

(2.33)

$$s = 1 - \frac{2 \cdot (\text{form length}) \cdot (a+b)}{\pi \cdot (\text{turn diameter}) \cdot n \cdot K_n}$$

(2.34)

$$L_0 = \frac{(n \cdot \pi \cdot \text{turn diameter})^2 \cdot 2.54 \cdot 10^{-9}}{\text{form length}}$$

(2.35)

$$L = L_0 \cdot K_n \cdot s \quad (H) \tag{2.36}$$

The value  $L_0$  is the inductance of a closely wound coil with a flat strip (wire diameter = 0). The value  $K_n$  is the Nagaoka correction factor and is used when the wire length is not much larger than the turn diameter. The value *s* is the current sheet correction factor and is needed when there is appreciable space between wire turns. Because  $L_0$  is not dimensionless, the lengths must be given in terms of inches. An example given in Ref. [11] illustrates the use of these expressions:

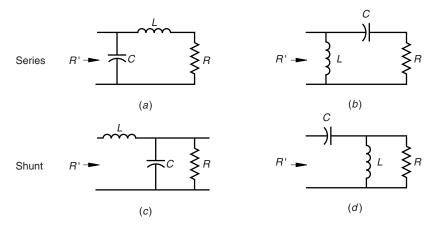

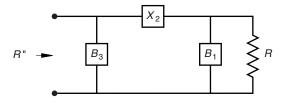

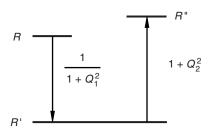

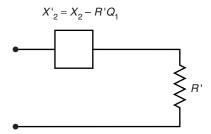

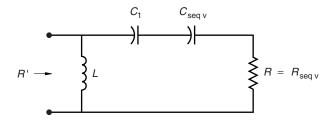

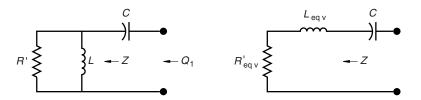

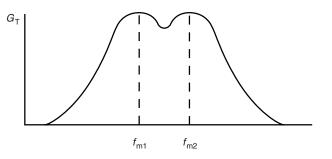

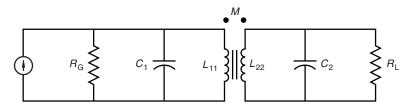

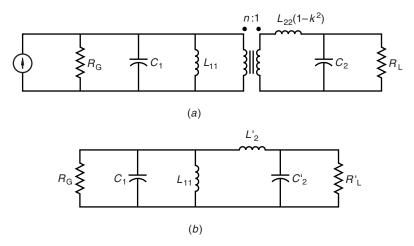

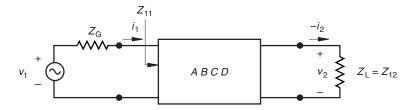

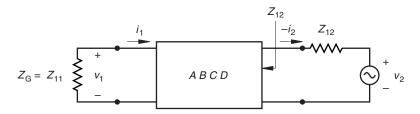

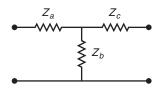

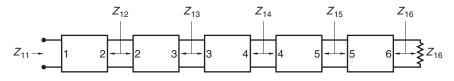

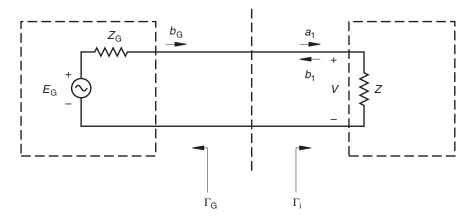

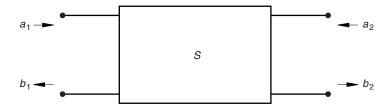

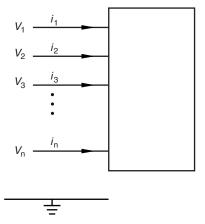

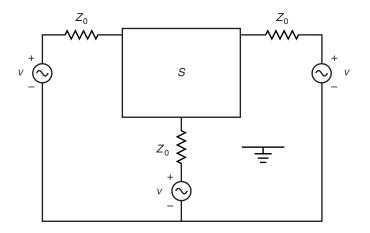

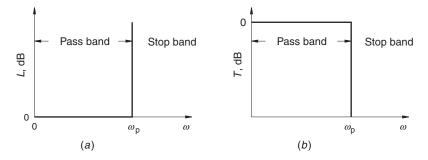

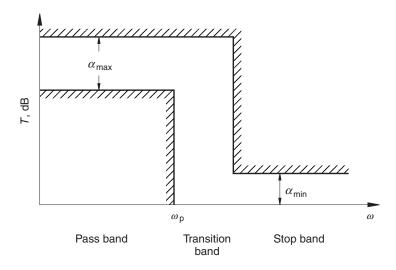

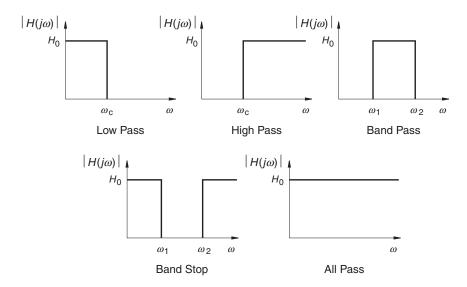

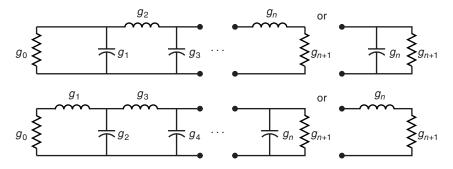

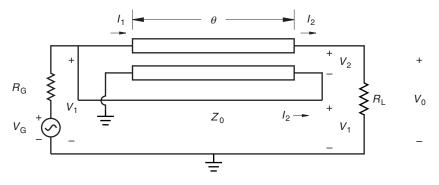

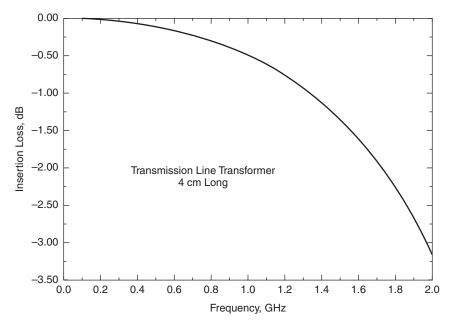

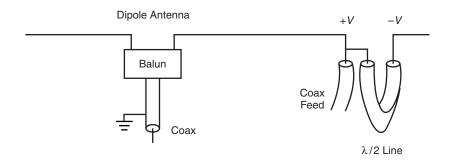

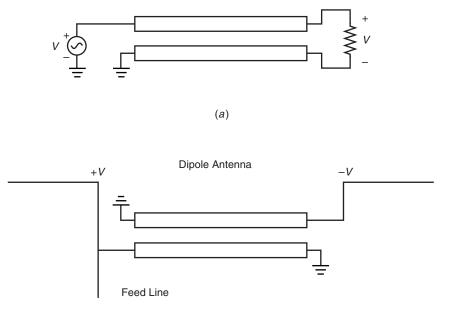

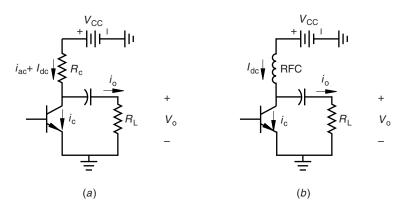

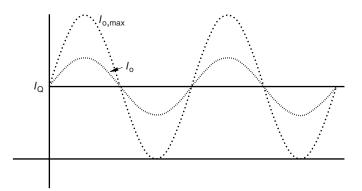

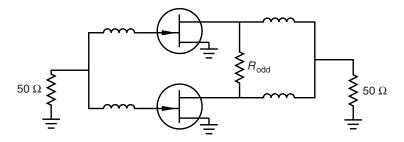

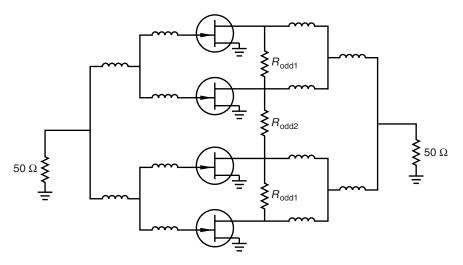

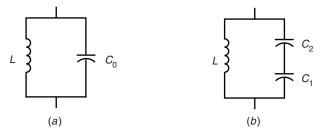

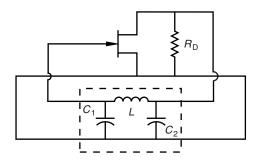

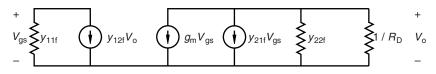

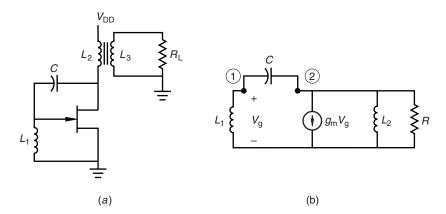

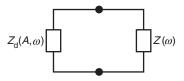

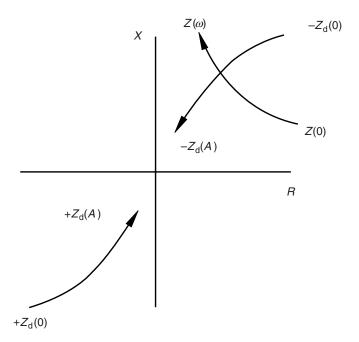

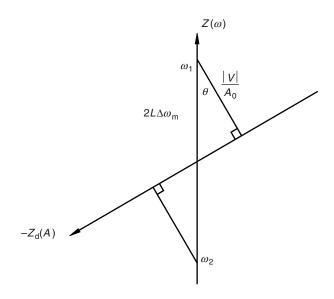

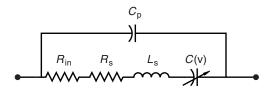

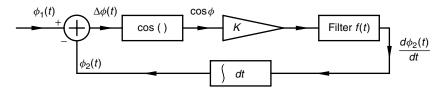

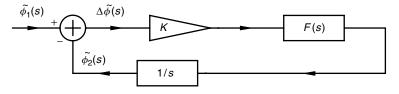

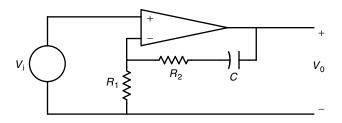

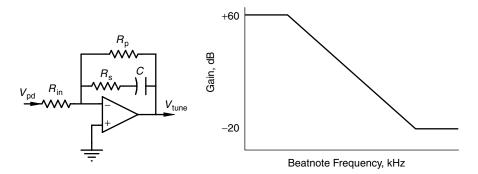

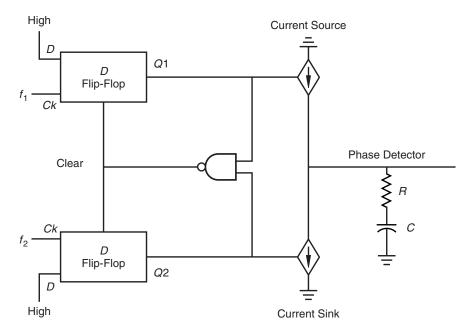

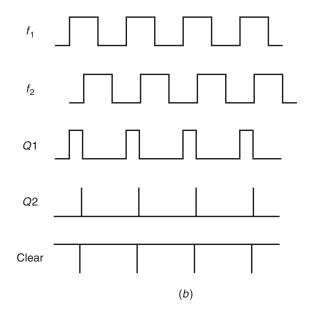

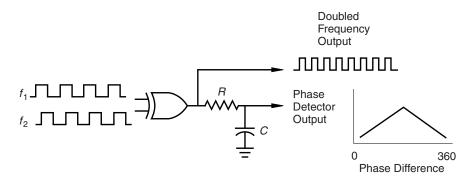

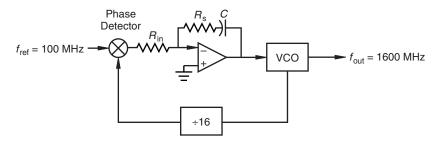

Pitch =  $0.0267 \ (n = 15)$ Wire diameter = 0.0187 in. Turn diameter = 0.2187 in. x = 0.5467 $K_n = 0.8035$ a = 0.1912b = 0.2857s = 0.954 $L_0 = 674$  nH L = 516.8 nH